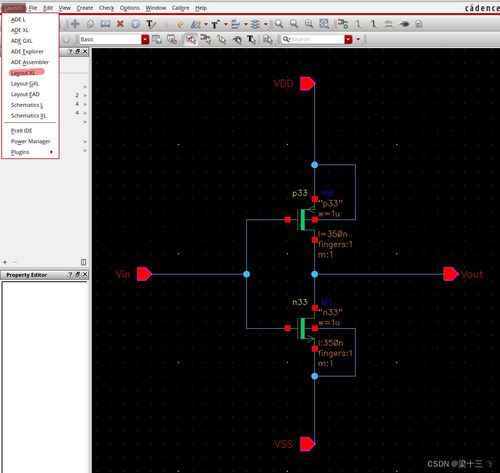

在集成電路設計流程中,完成電路原理圖設計后,最重要的環節就是版圖(Layout)設計和后續的仿真驗證。本文將基于Cadence Virtuoso平臺,詳細介紹反相器從Layout繪制到后仿真的完整流程。

一、反相器Layout設計

1. 創建Layout視圖

在Library Manager中,為之前設計的反相器電路創建Layout視圖。使用快捷鍵『Ctrl+N』新建cell view,選擇『Layout』類型。

- 版圖繪制要點

- 層次選擇:根據工藝文件(pdk)要求,正確選擇各層(如N阱、有源區、多晶硅、金屬等)

- 尺寸匹配:PMOS和NMOS的尺寸要與原理圖設計完全一致

- 接觸孔布置:合理布置源極、漏極和柵極的接觸孔

- 電源布線:VDD和GND使用高層金屬,確保良好連接

3. 具體繪制步驟

(1) 繪制N阱區域,包含PMOS管

(2) 繪制P+和N+注入區

(3) 布置多晶硅柵極,確保柵長與設計一致

(4) 添加金屬1連接,形成完整電路

(5) 添加輸入輸出端口標識

二、DRC檢查

完成Layout后必須進行DRC(設計規則檢查):

- 在Virtuoso界面選擇『Verify』→『DRC』

- 設置正確的工藝規則文件

- 檢查并修正所有DRC錯誤

- 確保版圖符合代工廠的工藝要求

三、LVS驗證

LVS(版圖與原理圖比對)確保Layout與Schematic一致:

- 運行LVS工具

- 檢查網絡匹配和器件匹配

- 解決不匹配問題,直至通過驗證

四、寄生參數提取

使用PEX(寄生參數提取)工具:

- 提取版圖中的寄生電阻、電容

- 生成包含寄生效應的網表文件

- 為后仿真提供準確的電路模型

五、后仿真分析

- 創建后仿真配置

- 使用ADE L設置仿真環境

- 加載PEX提取的網表

- 設置與前仿真相同的激勵和參數

- 關鍵性能指標對比

- 傳輸特性曲線

- 開關閾值電壓

- 上升/下降時間

- 傳播延遲

- 功耗分析

- 結果分析要點

- 對比前仿真與后仿真結果差異

- 分析寄生效應帶來的性能影響

- 評估版圖布局的優化空間

六、常見問題與解決

- DRC錯誤:檢查最小間距、寬度等規則

- LVS不匹配:確認器件尺寸、連接關系

- 后仿真性能下降:優化布線、減少寄生

反相器的Layout設計和后仿真是IC設計中的重要環節,通過嚴格的DRC/LVS檢查和準確的寄生參數提取,可以確保設計在實際制造中的可靠性。建議初學者在完成每個步驟后都仔細檢查,積累版圖設計經驗。